积层压敏电阻的工作原理

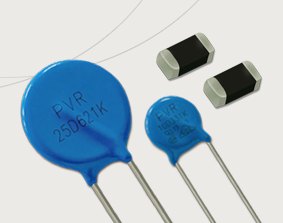

积层压敏电阻(MLV, Multilayer Varistor)是通过将多个压敏陶瓷层与金属电极交替沉积并高温烧结而成的片式元件。其核心材料为氧化锌(ZnO)基复合陶瓷,具有显著的非线性伏安特性。

非线性伏安特性详解

当施加电压低于阈值时,电阻值极高,几乎不导电;一旦电压超过临界点(如1.0~2.0倍额定电压),电阻急剧下降,形成低阻通路,将过电压能量泄放至地线,从而保护后级电路。

JMV-C系列的优势分析

- 体积小、集成度高:尺寸可做到1.6mm×1.6mm,适合高密度PCB布局。

- 低漏电流:在额定电压下漏电流低于1μA,减少功耗。

- 良好的温度稳定性:工作温度范围可达-55℃ ~ +125℃,适应严苛环境。

- 高可靠性测试认证:通过UL、IEC、AEC-Q200等国际认证,满足汽车电子需求。

安装与使用注意事项

1. 避免机械应力:焊接时需控制热冲击,推荐使用低温回流焊。

2. 正确布局:尽量靠近被保护电路入口,缩短引线长度以减少感应电压。

3. 定期检查:长期运行后可能因多次浪涌导致性能衰减,建议定期检测其压敏电压变化。

4. 注意并联使用:若需更高耐流能力,可并联多个器件,但需考虑均流问题。

未来发展趋势

随着物联网设备普及,对小型化、高可靠性的过压保护元件需求激增。JMV-C积层压敏电阻正朝着更高耐压等级、更低寄生电感、更强抗静电能力方向发展,预计将在新能源汽车、智能电网等领域发挥更大作用。