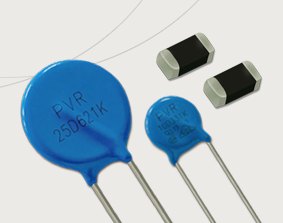

JMV-S积层压敏电阻概述

JMV-S积层压敏电阻是一种高性能的电子元件,广泛应用于电路保护领域。其核心特点是采用积层(Multilayer)结构设计,通过多层陶瓷材料与金属电极交替堆叠而成,具有优异的电压抑制能力和快速响应特性。

一、结构特点

- 积层式构造:利用精密印刷与烧结工艺,将多个压敏电阻单元集成于单一基板中,显著提升单位体积内的性能表现。

- 高密度集成:相比传统单体压敏电阻,积层结构使尺寸更小、安装空间更节省,适用于高密度PCB布局。

- 多层电极设计:每层均设有导电电极,实现均匀电流分布,降低局部过热风险。

二、主要技术参数

| 参数 | 典型值 |

|---|---|

| 额定电压(VDC) | 100V ~ 600V |

| 冲击耐受能力 | 10kA (8/20μs) |

| 响应时间 | ≤1ns |

| 工作温度范围 | -40°C ~ +125°C |

三、应用场景

JMV-S积层压敏电阻因其出色的瞬态过压抑制能力,被广泛应用于:

- 家用电器中的电源输入端保护(如空调、洗衣机)

- 工业控制设备的浪涌防护

- 通信设备与数据中心的信号线路保护

- 新能源汽车充电桩及车载电子系统

四、优势总结

综合来看,JMV-S积层压敏电阻具备以下核心优势:

- 体积小巧,适合SMT贴装

- 响应速度快,有效防止瞬态过压损坏

- 可靠性高,可承受多次冲击而不失效

- 符合RoHS与无铅环保标准