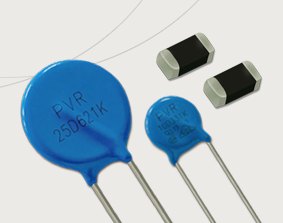

积层压敏电阻JMV-S的制造工艺解析

JMV-S系列积层压敏电阻采用先进的多层陶瓷厚膜印刷与高温烧结技术,是现代电子元器件小型化与高性能化的典范。其制造流程高度自动化,确保了产品的一致性与可靠性。

1. 关键制造步骤

- 浆料制备:以高纯度氧化锌为主料,添加微量金属氧化物(如Bi₂O₃、CoO、MnO₂)形成非线性伏安特性。

- 多层叠印:通过精密丝网印刷,在陶瓷基板上逐层打印电极与功能层,层数可达数十层。

- 高温共烧:在1200℃以上高温环境下完成致密化烧结,实现层间良好导电连接。

- 终端处理:采用镀镍或镀锡工艺增强焊接性能与耐腐蚀能力。

2. 技术创新点

- 纳米级颗粒控制:通过纳米粉体技术优化晶粒分布,提升击穿电压均匀性。

- 自修复机制:部分型号具备轻微过压后自我恢复能力,降低失效风险。

- 环保无铅工艺:符合RoHS和REACH法规要求,支持绿色制造。

3. 市场应用与未来趋势

随着物联网(IoT)、智能电网和电动汽车的快速发展,对小型化、高可靠性的过压保护器件需求激增。JMV-S积层压敏电阻凭借其卓越性能,正逐步替代传统片状压敏电阻。

预计在未来五年内,该系列产品在以下领域将实现快速增长:

- 智能家居设备中的电源保护模块

- 5G基站射频前端的瞬态抑制

- 储能系统(如锂电池组)的电压均衡与安全防护

- 医疗电子设备的电磁兼容设计

4. 选购与维护建议

为确保长期稳定运行,建议:

- 避免在潮湿或强酸碱环境中使用

- 定期检查是否有外观开裂或变色现象

- 在雷暴多发区域增加冗余保护设计

- 优先选择带有认证标识(如UL 1449、IEC 61051)的产品